新思科技DesignWare 112G Ethernet PHY IP经验证可用于5nm制程高性能计算SOC

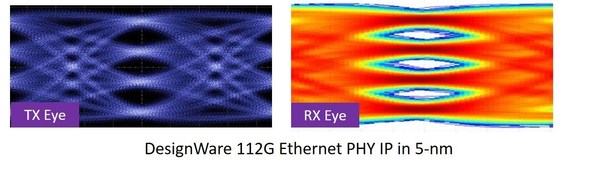

(全球TMT2021年2月22日讯)新思科技(Synopsys, Inc.)近日宣布, DesignWare®112G EthernetPHY IP已获得在5nm FinFET工艺上的硅认证,具有显著的性能、功率和面积优势。得益于DesignWare 112G以太网PHY的面积效率,开发者能够使用可感知布局的IP核来优化高密度的片上系统(SoC),通过最大限度地在裸片的四角进行堆叠和布局来提高边带宽。为了提高性能,DesignWare 112G PHY在大于40dB的通道中展示了前向纠错后的零误码率,同时具有低于5 pJ/bit的节能效果。

新思科技全面的112G以太网PHY解决方案结合了自身的布线可行性研究、封装基板指南、信号和电源完整性模型以及深入的串扰分析,可实现快速可靠的SoC集成。DesignWare 112G以太网PHY是新思科技面向高性能云计算应用的综合IP产品组合的一部分,除此之外还包括广泛使用的协议如PCI Express ®、DDR、HBM、Die-to-Die、CXL和 CCIX。

文章评论(0)